Si estas buscando respuesta a esta pregunta, seguramente estés interesado en algún aspecto de la Inteligencia Artificial. La respuesta corta, técnica y de traducción literal es «Unidad de procesamiento neuronal» (Neural processing Unit) muy obvio. ¿lo necesito? ¿mi ordenador o teléfono lo tiene?

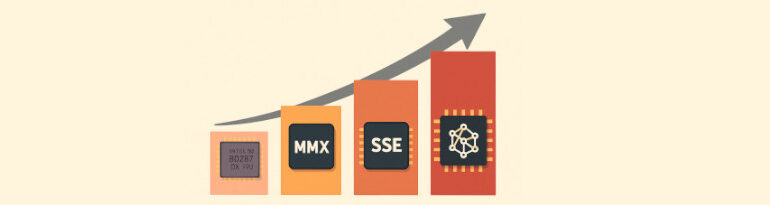

Vamos por partes, no es la primera vez que durante la evolución de una tecnología, aparecen unidades de apoyo especializadas para una tarea concreta. El concepto no es nuevo, en 1982 Intel añadió un coprocesador matemático (80287) para sus procesadores 286, utilizando el estándar IEEE 754 para coma flotante, lo que sería una FPU (Floating Point Unit) y que otros fabricantes también desarrollarían (AMD Am80C287, Cyrix 80C287…)

NOTA: si te interesa el tema de cálculos en coma flotante, échale un ojo al artículo 10^25 FLOPS

Desaparecieron en el momento que se integraron en el procesador principal (CPU, Central Processing Unit) a partir de los 80486DX en 1989, aunque algunos modelos venían sin FPU para abaratar costes (80486SX). Se simplifica el la arquitectura, el hardware, menos chips, menos espacio, menos consumos, más eficiencia y menores costes de producción a posteriori.

Lo mismo podríamos decir de las antiguas placas base con dos chips (northbridge y southbridge) a las que se fueron integrando sus funciones en la CPU y el resto aglutinando en un único chipset (llamarlo southbridge habiendo perdido el norte sonaba mal)

Con los años estos conjuntos de instrucciones especializadas se han ido ampliando para las arquitecturas x86 de Intel y AMD, muchas de ellas mediante técnica SIMD (Single Instruction, Multiple Data, una sola instrucción con múltiples datos simultáneamente) y ahora se añaden las NPU:

| Año | Nombre | Descripción |

|---|---|---|

| 1997 | MMX | MultiMedia eXtensions, SIMD para enteros, usado en video y audio |

| 1999 | SSE | Streaming SIMD Extensiones, SIMD para punto flotante en coma simple (32 bits), mejora multimedia y datos |

| 2000 | SSE2 | SIMD para punto flotante en doble precisión (64 bits) y enteros. Reemplazó y amplió MMX. |

| 2004 | SSE3 | Mejora SSE2. Nuevas instrucciones para procesamiento de señales y multiproceso. |

| 2006 | SSSE3 | «Supplemental SSE3». Más instrucciones SIMD, útil para compresión, cifrado, etc. |

| 2007 | SSE4.1 | Mejoras para gráficos y multimedia. Muy usado en juegos. |

| 2008 | SSE4.2 | Añade instrucciones como CRC32 (útil en compresión, bases de datos y redes). |

| 2009 | AVX | Advanced Vector Extensions. Registros de 256 bits (el doble que SSE). Mejora para cálculos científicos y multimedia. |

| 2011 | FMA3 | Fused Multiply-Add. Multiplicación y suma en una sola instrucción. Mejora el rendimiento de cálculos matemáticos. |

| 2013 | AVX2 | AVX para enteros, soporte para operaciones de 256 bits más completas. Gran salto en rendimiento. |

| 2016 | AVX-512 | Registros de 512 bits. Usado en servidores, HPC (High Performance Computing), inteligencia artificial, etc. |

| 2017 | ANE | Primera NPU integrada en SoC por Apple para IA móvil (rostro, voz, fotos…) |

| 2018 | SHA | Instrucciones específicas para acelerar algoritmos de hash SHA-1 y SHA-256. |

| 2018 | Da Vinci | NPU de Huawei (kirin 980) enfocada en eficiencia para IA móvil |

| 2018 | Coral | Google Edge NPU para inferencia IA en móviles (también en Coral USB) |

| 2019 | Hexagon | NPU de Qualcomm para IA en sus SoC Snapdragon |

| 2020 | AMX | Intel Advanced Matrix Extensions. Aceleración para redes neuronales y matrices. |

| 2021 | Mediatek | APU en chips propios como Dimensity, similar a NPU |

| 2023 | Intel | Primera NPU integrada en procesadores híbridos (Meteor Lake) |

| 2024 | XDNA | Primera NPU integrada basada en Xilinx de AMD, Ryzen AI |

| 2024 | XDNA 2 | Segunda generación de NPU Ryzen AI |

| 2024 | ANE | Segunda NPU de Apple para Mac (M4) |

| 2025 | Ryzen AI | Tercera generación de NPU de AMD |

Así que si, estamos ante otra evolución de hardware y software donde estas pequeñas unidades tienen mucho que decir para acelerar la inferencia de redes neuronales, ¿No había ya suficientes tecnicismos hasta ahora?

La inferencia es la fase en la que el modelo de IA (ya entrenado previamente) se utiliza para hacer predicciones con nuevos datos, por ejemplo al ejecutar ResNet-50 (una red neuronal de clasificación de imágenes) donde subes una foto al sistema y es capaz de decirte que la foto es de un perro, ese proceso es inferencia.

Ejecutar las tareas matemáticas de una red neuronal para realizar este proceso requiere gran cantidad de multiplicaciones de matrices y operaciones no lineales, la NPU esta diseñada específicamente para:

- Procesar miles de multiplicaciones acumulativas (MAC, Multiply-Accumulate) por segundo

- Paralelización de operaciones.

- Ejecutar redes convolucionales (como ResNet) de forma más eficiente que una CPU

- Trabajar con datos comprimidos (int8, float 16…) para ahorrar energía y tiempo.

Si una CPU sin ningún tipo de aceleración dedicada podría hacer la inferencia en 0.5 segundos, la GPU en 0.05 segundos, la NPU podría hacerlo en 0.02 segundos por poner un punto de comparación con un consumo energéticos 5 veces menor.

Para comprobar si tu ordenador tiene NPU en Windows 11 de manera rápida, puedes ir al administrador de dispositivos y buscar «Neural processors» o desde el administrador de tareas en el apartado de rendimiento aparecerá como hardware adicional.

Si tienes dudas o quieres más información no dudes en contactar con nosotros.